AMD Zen 4 Ryzen 9 7950X and Ryzen 5 7600X Review: Retaking The High-End

by Ryan Smith & Gavin Bonshor on September 26, 2022 9:00 AM ESTAM5 Chipsets: X670 and B650, Built by ASMedia

Finally, let’s talk about the chipsets that are going to be driving the new AM5 platform. Kicking things off, we have the B650 and X670 chipsets, as well as their Extreme variations. Since AMD is starting the rollout of their new platform with their high-end CPUs, they are matching this with the rollout of their high-end chipsets.

For this week’s launch, the initial boards available are all from the X670 family. B650 boards will, in turn, be coming next month. We’ll break down the difference between the two families below, but at a high level, X670 offers more I/O options than B650. And while not strictly a feature of the chipset, the market segmentation is such that the bulk of high-end AM5 boards – those boards with a massive amount of VRMs and other overclocker/tweaker-friendly features – will be X670 boards.

That said, for simplicity’s sake we’re going to start with the B650 chipset, and build up from there.

| AMD AM5 Chipset Comparison | ||||

| Feature | X670E | X670 | B650E | B650 |

| CPU PCIe (PCIe) | 5.0 (Essentially Mandatory) | 4.0 (5.0 Optional) |

5.0 (Essentially Mandatory) | 4.0 (5.0 Optional) |

| CPU PCIe (M.2 Slots) | At Least 1 PCIe 5.0 Slot | |||

| Total CPU PCIe Lanes | 24 | |||

| Max Chipset PCIe Lanes | 12x 4.0 + 8x 3.0 | 8x 4.0 + 4x 3.0 | ||

| SuperSpeed 10Gbps USB Ports | 4 CPU + 12 Chipset or 4 CPU + 10 Chipset + 1 Chipset 20Gbps or 4 CPU + 8 Chipset + 2 Chipset 20Gbps |

4 CPU + 6 Chipset |

||

| DDR5 Support | Quad Channel (128-bit bus) Speeds TBD |

|||

| Wi-Fi 6E | Yes | |||

| CPU Overclocking Support | Y | Y | Y | Y |

| Memory Overclocking Support | Y | Y | Y | Y |

| Available | September 2022 | October 2022 | ||

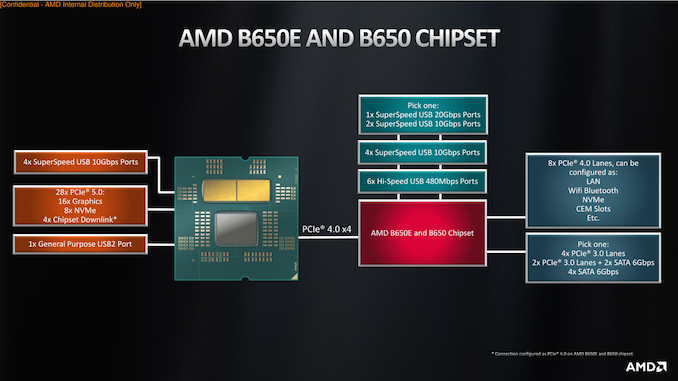

B650, AMD’s mainstream AM5 chipset, can best be thought of as a PCIe 4.0 switch with a bunch of additional I/O baked in. And as is typical for chipsets these days, several of the I/O lanes coming from the chipset are flexible lanes that can be reallocated between various protocols. Meanwhile, uplink to the CPU is a PCIe 4.0 x4 connection.

For PCIe connectivity, B650 offers 8 PCIe 4.0 lanes, which can either have PCIe slots or further integrated peripherals (LAN, Wi-Fi, etc) hung off of them. This and the uplink speed are both notable improvements over the B550 chipset, which was PCIe 3.0 throughout, despite Ryzen 3000/5000 offering PCIe 4.0 connectivity. So B650 has a lot more bandwidth coming into it, and available to distribute to peripherals.

There are also a quartet of PCIe 3.0 lanes which are shared with the SATA ports, allowing for either 4 PCIe lanes, 2 lanes + 2 SATA, or 4 SATA ports. Notably, the dedicated SATA ports found on the 500 series chipsets are gone, so motherboards will always have to sacrifice PCIe lanes to enable SATA ports. For the B650 this amounts to a net loss of 2 SATA ports, as the most ports it can drive without a discrete storage controller is 4.

Meanwhile on the USB front, motherboard vendors get more Superspeed USB ports than before. The chipset offers a fixed 4 10Gbps Superspeed ports, and then an additional output can be configured as either a single 20Gbps (2x2) port, or two 10Gbps ports. Finally, the chipset can drive a further 6 USB 2 ports, mostly for on-board peripheral use. There are no USB root ports limited to 5Gbps here, so all USB 3.x ports, whether coming from the CPU or the chipset, are capable of 10Gbps operation.

AMD has once again outsourced chipset development for this generation to ASMedia, who also designed the B550 chipset. AMD has not disclosed a TDP for the chipset, but like B550 before it, it is designed to run with passive cooling.

Outside of the technical capabilities of the B650 chipset itself, AMD is also imposing some feature requirements on motherboard makers as part of the overall AM5 platform, and this is where the Extreme designation comes in. All B650 (and X670) motherboards must support at least 1 PCIe 5.0 x4 connection for storage; Raphael has enough lanes to drive two storage devices at those speeds, but it will be up to motherboard manufacturers if they want to actually run at those speeds (given the difficulty of PCIe 5.0 routing).

Extreme motherboards, in turn, will also require that PCIe 5.0 is supported to at least one PCIe slot – normally, the x16 PCIe Graphics (PEG) slot. Non-extreme motherboards will not require this, and while motherboard vendors could technically do it anyhow, it would defeat the purpose of (and higher margins afforded by) the Extreme branding. Conversely, while AMD has been careful to toe a line about calling 5.0 slots outright mandatory on Extreme motherboards, it’s clear that there’s some kind of licensing or validation program in place where motherboard makers would be driving up their costs for no good reason if they tried to make an Extreme board without 5.0 slots.

It’s frankly more confusing than it should be, owing to a lack of hard and definite rules set by AMD; but the messaging from AMD is that it shouldn’t be a real issue, and that if you see an Extreme motherboard, it will offer PCIe 5.0 to its graphics slot. Past that, offering 5.0 to additional slots, bifurcation support, etc is up to motherboard vendors. The more PCIe 5.0 slots they enable, the more expensive boards are going to be.

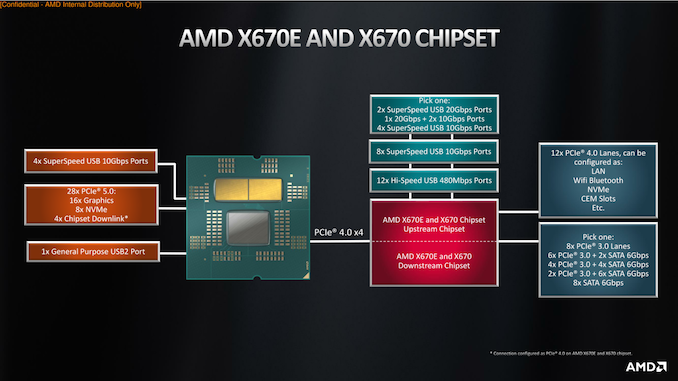

Meanwhile the high-end counterpart to the B650 chipset is the X670 chipset, which is pretty much just two B650 chipsets on a single board. While not explicitly confirmed by AMD, as we’ll see in the logical diagram for X670, there’s no way to escape the conclusion that X670 is just using B650 dies daisy chained off of one another to add more I/O lanes.

Officially, X670 is a two-chip solution, using what AMD terms the “downstream” and “upstream” chipsets. The upstream chip is connected to the CPU via a PCIe 4.0 x4 connection, and meanwhile the downstream chip is connected to the upstream chip via another PCIe 4.0 x4 connection.

By doubling up on the number of chips on board, the number of I/O lanes and options are virtually doubled. The sum total of the two chips offers up to 12 PCIe 4.0 lanes (the last 4 are consumed by the upstream chip feeding the downstream chip) and a further 8 PCIe 3.0 lanes that can be shifted between PCIe and up to 8 SATA ports.

Meanwhile on the USB front, there are now 8 fixed USB 2 ports and 8 fixed SuperSpeed USB 10Gbps ports. For USB flex I/O, motherboard makers can select from either 2 20Gbps ports, 1 20Gbps port plus 2 10Gbps ports, or 4 10Gbps ports.

And while this configuration adds more I/O lanes (and thus more I/O bandwidth), it should be noted that all of these I/O lanes are still gated behind the PCIe 4.0 x4 connection going back to the CPU. So the amount of backhaul bandwidth available between the chipsets and the CPU is not any higher than it is on B650. The name of the game here is flexibility; AMD is not designing this platform for lots of sustained, high-speed I/O outside of the CPU-connected x16 PCIe graphics slot and M.2 slots. Rather, it’s designed to have a lot of peripherals attached that are either low bandwidth, or only periodically need high bandwidths. If you need significantly more sustained I/O bandwidth, then in AMD’s ecosystem there is a very clear push towards Threadripper Pro products.

Finally, X670 Extreme (X670E) will impose the same PCIe 5.0 requirements as B650E. This means Extreme boards will offer PCIe 5.0 connectivity for at least one PCIe lane, while X670 boards are expected to come with just PCIe 4.0 slots. These will be the most expensive boards, owing to a combination of requiring two chipsets, as well as the extra costs and redrivers that go into extending PCIe 5.0 farther throughout a motherboard.

On that note, when discussing the new chipsets with AMD, the company did offer an explanation for why X670 daisy chains the chipsets. In short, daisy chaining allows for additional routing – the downstream chipset can be placed relative to the upstream chipset, instead of relative to the CPU (and PCIe devices then placed relative to the chipsets). In other words, this allows for spreading out I/O so that it’s not all so close to the CPU, making better use of the full (E)ATX board. As well, hanging both chipsets off of the CPU would consume another 4 PCIe lanes, which AMD would rather see going to additional storage.

205 Comments

View All Comments

Freeb!rd - Monday, September 26, 2022 - link

This paragraph reads like someone having a stroke while writing it..."Although this is overridable through manually overclocking with a maximum TJ Max of up to 115°C, it’s key tovitalte that users will need to use more premium and aggressive cooling types to squeeze every last drop of performance from ZAMD intended thistended when designing Zen 4, and as such, has opted not to bundls own CPU coolers with the retail packages."

and someone's spell checker is broken.

gryer7421 - Monday, September 26, 2022 - link

It reads like a GTP-3 BOT .... :(Threska - Monday, September 26, 2022 - link

We now know "Zencally " is a word.Gavin Bonshor - Monday, September 26, 2022 - link

Hi, yeah something screwy happened, but it's fixed now. Apologies. I think it may be time to update to a new system, and software. This isn't the first time it's jumbled stuff up for me.Cow86 - Monday, September 26, 2022 - link

I wish I could say that all the errors in the article are fixed, but that very paragraph even still has several (big) errors in it... A missing letter is one thing, half a sentence just missing and going into the next is another.herozeros - Monday, September 26, 2022 - link

Keep the copy editor awake, or fire them. Grammar/syntax/CMS error, it doesn't matter if it gives me a headache reading this.Ryan Smith - Monday, September 26, 2022 - link

Unfortunately we're having to do this kind of live. It's been a very busy past two weeks and we haven't had as much time to prepare as we like. So most of what you're seeing is first-draft copy, which I'll get around to editing as I can.Digital publications do not employ dedicated copy editors any more. They have all been let go for cost efficiency reasons.

flyingpants265 - Monday, September 26, 2022 - link

What? Come on now.Hifihedgehog - Monday, September 26, 2022 - link

@flypants265: It's kind of like Microsoft who got rid of their QA team and made all of their developers honorary QA tests. They can't help it that their leadership is being stupid. Don't blame Ryan or Gavin. Blame these greedy cheapskates that likewise didn't want to pay Ian Cutress enough to want to stay.Hifihedgehog - Monday, September 26, 2022 - link

*QA testers