AMD Zen 4 Ryzen 9 7950X and Ryzen 5 7600X Review: Retaking The High-End

by Ryan Smith & Gavin Bonshor on September 26, 2022 9:00 AM ESTMore I/O For AM5: PCIe 5, Additional PCIe Lanes, & More Displays

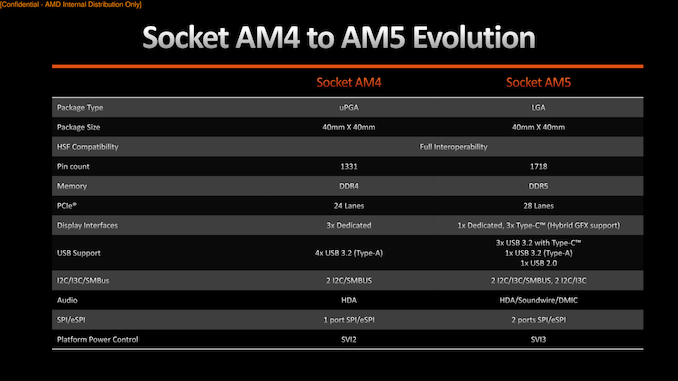

AMD’s other big expenditure using socket AM5’s additional pins is on I/O support. While AM4 already supported a fair bit of I/O, including 24 PCIe lanes, 3 displays, and 4 Superspeed USB ports, there was still room for improvement. So for AM5, AMD has increased the amount of I/O and the flexibility offered with the platform.

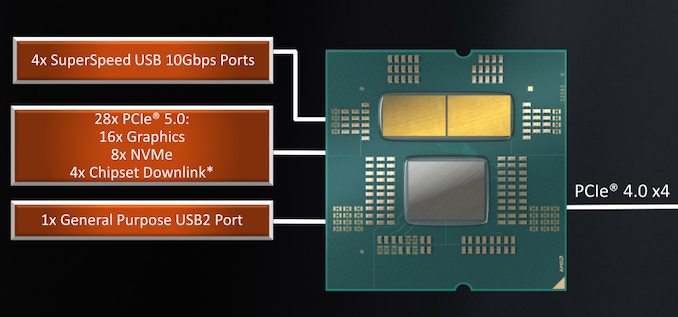

The biggest change here is that the AM5 socket now provides for 28 lanes of PCIe, a net gain of 4 lanes. More significantly still, PCIe 5.0 is now supported (at least on the Ryzen 7000 “Raphael” processors), doubling the bandwidth of all of those PCIe lanes to a max of 4GB/sec/lane. Which gives the chip a maximum cumulative PCIe bandwidth of 112GB/sec in each direction.

In practice, those additional lanes are intended for NVMe drives, giving AM5 a second x4 connection to drive a second NVMe drive; though we have seen some motherboard designs where vendors are stealing the second x4 for a PCIe 5.0 x4 slot. Past that, things look a lot like AM4, with 16 PCIe lanes to directly drive one or more PCIe slots, and then 4 lanes for hooking up the chipset.

Meanwhile, the updated socket also offers enough pins for the CPU to drive 4 Superspeed USB 3.x ports, and a USB 2 port. The USB 2 port is new for this generation, and meanwhile 3 of those USB 3 ports now also support the USB Type-C connector, unlike AM4 which could only natively drive Type-A ports. As a result, AM5 CPUs can drive a total of 3 Superspeed Type-C ports, a fourth Superspeed Type-A port, and then the aforementioned USB 2 port.

There has been one regression, however, and that is SATA support. Whereas AM4 CPUs could drive a mix of NVMe and SATA drives (up to 2 SATA + a PCIe x2 for NVMe), AM5 is purely PCIe. So there is no native SATA support on the CPU, and supplying that will come from the chipset.

To visualize this, we’ll use part of the AM5 chipset diagram. We’ll go more into the specifics of the chipsets in a bit, but lays out what is wired to the CPU, and what will need to be wired to the chipset. Of note there, the current chipsets only use PCIe 4.0 connectivity to the Ryzen CPU, so the current generation of chipsets will not be making full use of the bandwidth capabilities of the CPU itself.

Which with the addition of PCIe 5.0 support to the platform, is going to be a recurring theme. While AMD has baked in 5.0 support into the Raphael CPUs, it’s up to motherboard vendors to actually make it so. Compared to PCIe 4.0, 5.0 has much tighter signal integrity requirements (the signaling frequency has been doubled), which at least at this time, makes PCIe 5.0 expensive to implement. A very well-designed motherboard is required with impeccable traces, and on top of that the overall short throw of PCIe 5.0 means that retimers/redrivers become necessary rather quickly. So while AM5 can support PCIe 5.0 throughout, the reality is that we’re still going to see a lot of PCIe 4.0 in use even in higher-end motherboards.

As for the necessity of PCIe 5.0 overall, thus far AMD is primarily focused on what it means for NVMe drive speeds. The first generation of PCIe 5.0-enabled consumer SSDs are expected to land a bit later this year, and they should be able to hit sequential burst transfer rates above the limits of PCIe 4.0 (~7GB/sec).

Past that, NVIDIA’s newly announced Ada Lovelace architecture GeForce RTX 40 series video cards do not support PCIe 5.0. So while we’re awaiting AMD to announce their RDNA 3-based product lineup later this year, regardless of what AMD does, the bulk of video cards sold next year are not going to use PCIe 5.0. So there is a bit less pressure on motherboard manufactures (and motherboard buyers) to get boards that support PCIe 5.0 to anything beyond a couple of M.2 slots.

Finally, in conjunction with the USB I/O changes, AM5 also introduces some display I/O changes. Whereas AM4 could directly drive up to 3 displays, AM5 brings this to 4. Specifically, AM5 offers one dedicated display output (which will generally be allocated to HDMI), while the other 3 display outputs are available over those 3 USB Type-C ports as DisplayPort alt mode. It’ll be up to motherboard manufacturers if they want to expose any of these USB-C root ports as physical USB-C ports or as DisplayPorts, but so far from the motherboard designs we’ve seen, the former is more common (though certainly not universal).

Anticipating a shift to more USB Type-C displays, AMD is also implementing what they call “hybrid graphics” support on AM5. Unlike previous products where this referred to linking up the integrated graphics with a discrete GPU in CrossFire mode, this time around it refers to being able to being able to use the mobo/iGPU’s display outputs to drive a monitor while using a dGPU to render content. This is largely lifted from AMD’s laptop technologies, where similar techniques are used to allow the dGPU to be powered down when it’s not in use. In the case of desktop processors, this just means every display output will work, regardless of whether it’s plugged into ports coming from the CPU or a discrete video card.

It’s also worth noting that AM5 is bringing a few other, more minor updates to other comms protocols. Among these is support for MIPI’s (relatively) new I3C chip-to-chip signaling standard, which will ultimately be supplanting the long-used I2C standard. As well, AM5 doubles the number of I2C/I3C ports available, bringing the total to 4 ports. The platform also adds a second (enhanced) Serial Peripheral Interface (eSPI/SPI) port, and on the audio front, adds support for the Digital Mic and MIPI’s Soundwire standard for low-cost audio peripherals.

205 Comments

View All Comments

Freeb!rd - Monday, September 26, 2022 - link

This paragraph reads like someone having a stroke while writing it..."Although this is overridable through manually overclocking with a maximum TJ Max of up to 115°C, it’s key tovitalte that users will need to use more premium and aggressive cooling types to squeeze every last drop of performance from ZAMD intended thistended when designing Zen 4, and as such, has opted not to bundls own CPU coolers with the retail packages."

and someone's spell checker is broken.

gryer7421 - Monday, September 26, 2022 - link

It reads like a GTP-3 BOT .... :(Threska - Monday, September 26, 2022 - link

We now know "Zencally " is a word.Gavin Bonshor - Monday, September 26, 2022 - link

Hi, yeah something screwy happened, but it's fixed now. Apologies. I think it may be time to update to a new system, and software. This isn't the first time it's jumbled stuff up for me.Cow86 - Monday, September 26, 2022 - link

I wish I could say that all the errors in the article are fixed, but that very paragraph even still has several (big) errors in it... A missing letter is one thing, half a sentence just missing and going into the next is another.herozeros - Monday, September 26, 2022 - link

Keep the copy editor awake, or fire them. Grammar/syntax/CMS error, it doesn't matter if it gives me a headache reading this.Ryan Smith - Monday, September 26, 2022 - link

Unfortunately we're having to do this kind of live. It's been a very busy past two weeks and we haven't had as much time to prepare as we like. So most of what you're seeing is first-draft copy, which I'll get around to editing as I can.Digital publications do not employ dedicated copy editors any more. They have all been let go for cost efficiency reasons.

flyingpants265 - Monday, September 26, 2022 - link

What? Come on now.Hifihedgehog - Monday, September 26, 2022 - link

@flypants265: It's kind of like Microsoft who got rid of their QA team and made all of their developers honorary QA tests. They can't help it that their leadership is being stupid. Don't blame Ryan or Gavin. Blame these greedy cheapskates that likewise didn't want to pay Ian Cutress enough to want to stay.Hifihedgehog - Monday, September 26, 2022 - link

*QA testers